# Image Transform Using 2-D DCT Architecture For JPGE Encoder

Sekhar Suman<sup>#1</sup>, Ajay Kumar Barapatre<sup>\*2</sup>

#Research Scholar Department of ECE VIT, RKDF University

#Asst. Prof & Head, Department of ECE, VIT, RKDF University

Airport Bypass Road, Gandhi Nagar, Bhopal (MP), India

<sup>1</sup>suman.sekhar@gmail.com

<sup>2</sup>barapatre.ajay@yahoo.co.in

Abstract — picture compression is restricting the scale in bytes of a designs document without corrupting the nature of the photograph to an inadmissible level. The diminishment in document measure enables more images to be placed away in a given measure of circle or memory space. It additionally decreases the time required for pictures to be sent over the Internet or downloaded from Web pages. JPEG and JPEG 2000 are two critical procedures applied for image pressure. A VLSI Technology have Alsobeen used for the 2D-DCT and 2D-IDCT. This VLSI design is playing out the JPEG image compression and picture compression utilizing Low many-sided quality DCT.

by means of normalizing the estimations of its pixels, any image can be considered as a fuzzy framework (connection) which is subdivided in sub-networks (perhaps square) called fragments. Each square is compacted with the method of the discrete fuzzy change of a capacity in two factors and progressively it is decompressed through the related opposite fuzzy change. The decompressed fragments are recomposed for the recreation of the image, whose quality is assessed by figuring the PSNR (Peak Signal to Noise Ratio), MSE(Mean Square Error) concerning the first picture.

**Keywords** — JPEG, JPEG 2000, 2D-DCT, 2D- IDCT, fuzzy transform, PSNR (Peak Signal to Noise Ratio), MSE (Mean Square Error).

#### I Introduction

What is data compression? Data compression is one of the enabling technologies of the multimedia revolution, data compression is a key to rapid progress being made in information technology. Data compression is the process of converting data files into smaller size for increasing efficiency of storage and transmission. The digital data have become an important source of information in the present world of communication systems.

why do we need data compression? JPEG (Joint Photographic Experts Group) and MPEG (Moving Pictures Experts Group) are compression standards for representing still images and videos. Data compression algorithms are utilized in those standards to lessen the range of bits required to represent an image or a video sequence. Compression is the process of representing information in a compact form. Data compression treats information in digital form, that's, as binary numbers represented with the aid of bytes of data with very large data units. Fox example, a single small 4" x 4"

size color photagraph, scanned at 300 dots per inch (dpi) with 24 bits/pixel of real color, will produce a file containing more than 4 megabytes of data. At least three floppy disks are required to store such a picture. This image requires more than one minute for transmission by a typical transmission line (64k piece/second ISDN). That is the reason large image documents remain a major bottleneck in a conveyed environment. Although increasing the bandwidth is a possible solution, the relatively excessive cost makes this a great deal much less attractive. Therefore, compression is a necessary and essential method for creating image files with manageable and transmittable sizes.

#### II IMAGE COMPRESION AND RECONSTRUCTION

the image compression standard are categorized in the three basic data redundancies which are as follows:-

- 1. Spatial redundancy due to the correlation between neighbouring pixels.

- 2. Spectral redundancy due to correlation between the color components.

- 3. Psycho-visual redundancy due to properties of the human visual system.

The spatial and otherworldly redundancies are available in mild of the fact that precise spatial and unearthly examples among the pixels and the shading segments are normal to each other, even as the psycho-visual repetition starts from the way that the human eye is uncaring to certain spatial frequencies. The point here is to acquire a satisfactory portrayal of computerized picture at the same time as saving the fundamental data contained in that spacific informational collection.

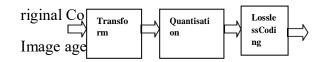

The problem faced by image compression is very easy to define, as demonstrated in figure 1.1.

Fig. 1.1

#### 1.1 IMAGE COMPRESSION METHODS:

Two types of image compression methods which is defined as follows:

- Lossy compression

- Lossless compression

# 1.1.1 Lossy Compression:-

A lossy Compression approach is one where compacting information and afterward decompressing it recovers information that is not pretty the same as the first, yet is adequately close to be helpful somehow. Lossy pressure is most regularly used to pack sight and sound information (sound, video, nevertheless pictures), particularly in applications, for example, gushing media and web communication. by differentiate, lossless stress is required for content and information documents, for example, bank records, content articles, and so forth. tons of the time it's far worthwhile to make an ace lossless document which would then be able to be applied to create packed records for various purposes; for instance a multi-megabyte document can be utilized at full size to deliver a full-page promotion in a shiny magazine, and a 10 kilobyte lossy duplicate made for a little picture on a website page. for instance a multi-megabyte document can be utilized at complete length to supply a fullpage promotion in a vibrant magazine, and a 10 kilobyte lossy duplicate made for a little photo on a website page. JPEG Compression, Wavelet Compression, Fractal Compression are the Strategies for lossy Compression.

# 1.1.2 Lossless Compression :-

The objective of lossless picture compression is to speaokay to a photo motion with the littlest conceivable number of bits without loss of any data, in this manner accelerating transmission and limiting stockpiling conditions. Lossless Image Compression is a class of image compression calculation that enables the correct unique Image to be reproduced from packed image. The quantity of bits speaking to the flag is normally communicated as a normal number of bits per test for still pictures, and normal number of bits every second for video. Some image file formats, notably PNG, use only lossless compression.

Huffman encoding, Arithmetic coding, Run-length coding are the methods for Lossless Compression.

#### 1.2 Performance Measures of Image Compression:-

The measurement of performance of data compression scheme by the following three parameters. These are:

I. Compression efficiency

II.Complexities

III. Distortion measurement for lossy compression Compression efficiency is measured through compression ratio (CR). The CR can be defined as the ratio of the data length (number of bits) of the original data to the dimensions(size) of the corresponding compressed data. The data operations include additions, subtractions, and multiplication, divisions and shift operations. In encoding and decoding operation the complexities of a digital data compression algorithms are measured by a number of data operations required. The amount of information lost on the reconstruction of the original signal measured by the distortion measurement in the case of lossy compression

algorithm. The performance measurement parameter; Mean Square Error (MSE) and Signal to Noise Ratio (SNR) is also used to measure the performance of the lossy compression algorithms. These measurement criteria are often used for 1D data. For image data (2D) compression, the SNR is replaced by a parameter known as peak signal to noise ratio (PSNR). The same measurement parameters are also used for I-D data. For 2-D (Image Data) Compression, the parameter SNR is replace by parameter known as peak signal to noise ratio (PSNR). distortion measurement is the aslo represented throught percentage of energy retained in the compressed data.

### III TRANSFOMING AGLORITHM:-

The image compression method using Discrete Cosine Transform, is presented in this paper. Orthogonal approximation using Discrete Cosine Transform and Low complexity Discrete Cosine Transform is also discussed for image compression. The image compression using Discreate Cosine Transform is the well known JPEG technique [3-4]. The image compression technique given by Renato J. Cintra&Fábio M. Bayer [4] is another image compression algorithm is using the Orthogonal approximation DCT.

## 3.1 Image compression using DCT:-

JPEG is the most popular and effective method for still image compression. It is the international standard for effective compression. The name JPEG stands for Joint Photographic Experts Group, the name of the committer who created the JPEG standard [3-4]. In JPEG compress an image in to a stream of bytes and decompress it again to generate the original image back.

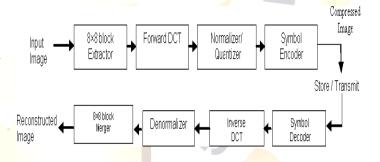

Fig. 3.1:- Schematic diagram of JPEG compression

As per the user requirement JPEG can adjust the compression ratio and the image quality. In the JPEG Process RGB (color representation) mode, is convert in to YUV and divide the file into 8 X 8 blocks. Transform the pixel information from the spatial domain to the frequency domain with the Discrete Cosine Transform. Quantize the resulting values by dividing each coefficient by an integer value and rounding off to the nearest integer.

# 3.2 Simulation Results for the JPEG Compression:-

For our effects, 4 test images are taken from the image database and resize them to a size of 256x256.

Fig 3.2 Test images (a) cameraman (b) lena (c) circuits (d) pappers.

# 3.3 Orthogonal Approximation Discrete Cosine Transform:

An orthogonal approximation for the 8-point discrete cosine transform (DCT) have the transformation matrix contains only zeros and ones; multiplications and bit shift operations are absent. Close spectral behaviour relative to the DCT was adopted as design criterion. The proposed algorithm is superior to the signed discrete cosine transform. It could also outperform state-of-the-art algorithms in low and high image compression scenarios, exhibiting at the same time a comparable computational complexity.

An adjustment matrix A that orthogonalizes B<sub>0</sub> is sought. Indeed, the referred orthogonalization matrix is given by:

$$\mathbf{A} = \sqrt{\mathbf{B0. B0T}} - \mathbf{1}$$

(3.1)

where the matrix square root is taken in the principal sense. This computation furnishes the diagonal matrix

A= diag

$$(1/2\sqrt{2}, 1/\sqrt{6}, 1/2, 1/\sqrt{6}, 1/2\sqrt{2}, 1/\sqrt{6}, 1/2, 1/\sqrt{6})$$

S = diag $(1/2\sqrt{2}, 1/\sqrt{6}, 1/2, 1/\sqrt{6}, 1/2\sqrt{2}, 1/\sqrt{6}, 1/2, 1/\sqrt{6})$ Therefore, the DCT matrix can be more adequately approximated by the following proposed matrix:.

$$\hat{\boldsymbol{B}}_{\text{orth}} = A.$$

Bo

Matrix **B**<sub>0rth</sub> possesses useful properties: i) it is orthogonal;

- ii) it inherits the low computational complexity of  $\widehat{\pmb{B}}$  orth; and

- iii) the orthogonalization matrix A is diagonal.

The image or any two dimensional signal can be transformed to the with the help of  $\widehat{B}$  orth the another domain

$$f(\boldsymbol{u},\boldsymbol{v}) \, \widehat{\boldsymbol{B}}_{\text{orth}} * f(\boldsymbol{x},\boldsymbol{y}) * \widehat{\boldsymbol{B}}_{\text{orth}} \quad \dots (3.2)$$

For the purpose of image compression, we have used the OA – DCT in the similar way as the DCT was used. The remaining methodology adopted is same for the OA-DCT that used for JPEG.

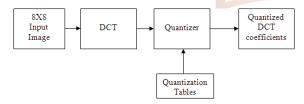

# 3.4 A New Modal for Image Compression Using DCT VLSI Architecture

A Novel VLSI Architecture for Image Compression Model Using Discrete Cosine Transform is prepented in this paper. The VLSI design can also be implemented Using Verilog HDL.

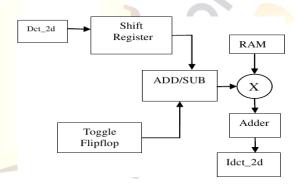

Fig. 3.3: Block diagram of DCT Process

The proposed hardware architecture was synthesized

the usage of RTL complier and it was mapped the usage of 180nm standard cells. The Simulation is done the use of Modelsim. The recreation comes about because of MATLAB and Verilog HDL are looked at. Point by means of point investigation for power and region was finished utilizing RTL compiler from CADENCE. in this process enter image is split into non-overlapping blocks of 8 x 8 pixels, and enter to the baseline encoder. Power utilization is lower to 1.027mW with least zone.

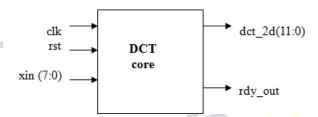

Fig. 3.4: Top level schematic for DCT core

DCT coefficients are generated by DCT transformation of the pixel data into a block of spatial frequencies. for the reason that pixels within the 8 x 8 neighbourhood typically have small variations in gray ranges, the output of the DCT will result in most of the block energy being stored in the lower spatial frequencies.

The adder/ subtractor is linked to CLK. For every clk, the adder/subtractor module alternately chooses addition and subtraction. This selection is done by the toggle flop. The output of the add/sub is fed into a multiplier whose other input is connected to stored values in registers which act as memory. at every CLK, The outputs of the 4 multipliers are added in the final adder. The yields from the snake within the second phase are the 2nd-DCT coefficients esteems given out inside the request wherein the data sources were perused in. At the point when 2d DCT calculation is over the rdy out flag goes excessive demonstrating the yield. The fig.3.3 shows the 1D-IDCT is implemented on the input DCT values. The output of this called the intermediate value is stopurple in a RAM. The

Fig 3.5:- IDCT Architecture

second 1D-IDCT operation is done on this stocrimson value to deliver the final 2D-IDCT output IDCT 2D.

The inputs are 12 bits extensive and the 2D-IDCT output are eight bits wide. 1st 1D section, the input signals are taken one pixel at a time within the order x00 to x07, x10 to x07 and so on up to x77. Those inputs are fed into an 8 bit

shift register. The outputs of the eight bit shift registers are registered at every 8th clock. This will enable us to signin(register) in 8 pixels (one row) at a time.

TABLE I: Characteristic of DCT and IDCT

| Feature      | DCT                   | IDCT                  |

|--------------|-----------------------|-----------------------|

| No. of cells | 6773                  | 8571                  |

| Block Size   | 8X8                   | 8X8                   |

| Latency      | 92 cycles             | 85cycles              |

| Power        | 1.0271 mW             | 1.261 mW              |

| Area         | 0.6281mm <sup>2</sup> | 0.7652mm <sup>2</sup> |

TABLE II: Performance Comparison

| DCT Architecture  | Power in mW | Area in mm <sup>2</sup> |  |  |  |  |  |

|-------------------|-------------|-------------------------|--|--|--|--|--|

| Proposed DCT core | 1.0271      | 0.6281                  |  |  |  |  |  |

| DCT Architecture  | 29.78       | 0.343                   |  |  |  |  |  |

| DCT core          | 29.92       | 0.569                   |  |  |  |  |  |

#### **IV DESIGN SIMULATION:-**

Fuzzy transform grew to become out to be very general and powerful. A function obtained by means of the inverse F-transform has satisfactory filtering properties which can be used to removing noise from images or from any other kind of data. F- transforms can be used for data compression. we will also show, how this approach can be applied to data compression and decompression.

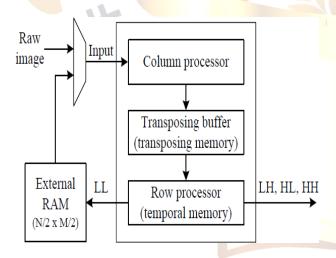

Fig 4.1: The overall 2-D DCT architecture

The given architecture performs the forward and inverse 2-D DCT transform within the column-row fashion. Fig 4.1 shows the overall 2-D DCT architecture, which includes three main components — the column processor, the transposing buffer and the row processor.

To carry out the one-stage decomposition for an NxM image, the given architecture executes the column processor,

the transposing buffer and the row processor simultaneously, where N and M represent the image top and width. Moreover, the row processor has to execute row-smart transform once enough column processed data are obtained to decrease the internal memory size. Thereafter, the MN/4 size external RAM is used to store the LL band output coefficients for the subsequent stage decomposition.

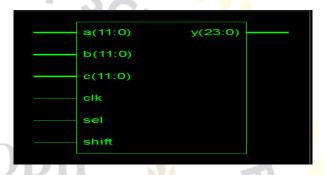

V SIMULATION RESULTS: The fig. 5.1 shows the schematic symbol of column processor in XILINX. This section deals with the simulation of column processor in XILINX ISE simulator.

Figure 5.1: Schematic Symbol of Column Processor in Xilinx

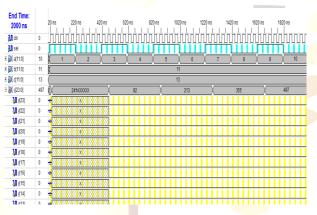

The fig 5.2 shows the Test Bench Waveform of 12 Bit Column Processor.

Figure 5.2 : Test Bench Waveform of 12 Bit Column

#### 5.1 Simulation Results of 16 Input Transposing Buffers:-

Fig.5.3: Technology Schematic of Transposing Buffer in Xilinx

This section deals with the simulation of Transposing Buffer in XILINX ISE simulator. The fig. 5.3 shows the schematic symbol of Transponding Buffer in XILINX.

The fig 5.4 shows the Test Bench Waveform of Transposing buffer in XILINX.

| End Time:<br>1000 ns |   | 50            | ns | 19 | 50 ns |     | 950 ns | ı | 350 ns | ll | 450 ns | 1 | 550 ns |   | 650 ns | 1 | 750 ns | 11 | 850 ns | 1 | 950 ns |

|----------------------|---|---------------|----|----|-------|-----|--------|---|--------|----|--------|---|--------|---|--------|---|--------|----|--------|---|--------|

| ⊞ 🙀 a[3:0]           | 1 |               |    |    |       |     |        |   |        |    |        | 1 |        |   |        |   |        |    |        |   |        |

| ⊞ <b>∭</b> b[3:0]    | 2 |               |    |    |       |     |        |   |        |    |        | 2 |        |   |        |   |        |    |        |   |        |

| ⊞ <b>∭</b> d[3:0]    | 3 |               |    |    |       |     |        |   |        |    |        | 3 |        |   |        |   |        |    |        |   |        |

| ⊞ <b>∭</b> d[3:0]    | 4 |               |    |    |       |     |        |   |        |    |        | 4 |        |   |        |   |        |    |        |   |        |

| ⊞ 🚮 e[3:0]           | 5 |               |    |    |       |     |        |   |        |    |        | 5 |        |   |        |   |        |    |        |   |        |

| ⊞ <b>∭</b> f(3:0]    | 6 | $\overline{}$ |    |    |       |     |        |   |        |    |        | 6 |        |   |        |   |        |    |        |   |        |

| ⊞ 💓 g[3:0]           | 7 |               |    |    |       |     |        |   |        |    |        | 7 |        |   |        |   |        |    |        |   |        |

| ⊞ <b>∭</b> h[3:0]    | 8 |               |    |    |       |     |        |   |        |    |        | 8 |        |   |        |   |        |    |        |   |        |

| ⊞ 💓 i(3:0]           | 9 |               |    |    |       |     |        |   |        |    |        | 9 |        |   |        |   |        |    |        |   |        |

| ⊞ <b>∭</b> Sel[3:0]  | 9 |               | 0  | χ  | 1     | χ   | 2      | χ | 3      | X  | 4      | X | 5      | χ | 6      | χ | 7      | X  | 8      | X | 9      |

| ∃ <b>[</b> [ y[3:0]  | 7 |               |    |    |       | 4h2 | !      |   |        |    | X      | 1 | X      | 5 | X      | 2 | X      | 6  | X      | 3 | 7      |

| <b>\II</b> y[3]      | 0 |               |    |    |       | 2   |        | - |        |    | _      |   |        |   |        |   |        |    |        |   |        |

| <b>\II</b> y[2]      | 1 |               |    |    |       | 1   |        | F |        | Ė  |        | Í |        | Ť |        |   |        | Ť  |        |   |        |

| <b>\1</b> 1 y(1)     | 1 |               |    |    |       | 1   |        | F |        | Ė  |        | ĺ |        |   |        | Ť |        | Ť  |        | T |        |

| <b>\II</b> y[0]      | 1 |               |    |    |       | 1   |        | F |        | Ė  |        | i |        | Ť |        |   |        |    |        | T |        |

Figure 5.4: Test Bench Waveform of Transposing Buffer in Xilinx

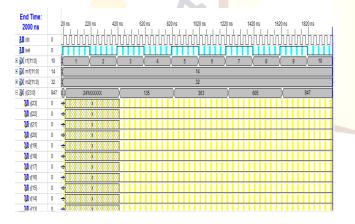

#### 5.2 Simulation Results of 12 Bit Row Processor:-

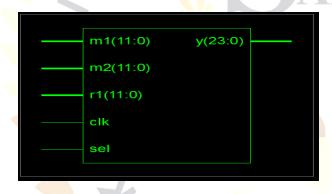

In this section we discuse 24 Bit 2X1 Demultiplexer in XILINX ISE simulator. The fig. 5.5 shows schematic symbol of 12 Bit Row processor in XILINX Simulator.

Figure 5.5:- Schematic Symbol of 12 Bit Row Processor in Xilinx

Fig 5.6: Test bench waveform of 12 Bit Row Processor in Xilinx

#### VI CONCLUSION:-

The main aim in the back of those strategies is to lessen the complexity as compacrimson with DCT method. Such as the primary makes use of a 'Discrete Cosine Transform' method for compression. The second uses a 'DCT Approximation' method for compression. The third uses a 'Low complexity 8×8 transform' method for compression.

we provide a novel lossly image compression technique. The main aim at the back of this method is to reduce the complexity and secondly to make the compression approach fast with a reasonable image compression. With this new method the compression and decompression method becomes enough faster. Without compression, the transmission time as well as the storage requirement could be large however inclusion of compression and reconstruction scheme reduces the storage requirement and data transmission time. The VLSI architecture for the 2DDCT and 2DIDCT has also been described on this chapter, that is a very good method for image compression. The image compression can also be performed the usage of the described VLSI architecture.

#### REFERENCE:

[1]Wei Zhang, Member, IEEE, Zhe Jiang, Zhiyu Gao, and Yanyan Liu, "An Efficient VLSI Architecture for Lifting-Based Discrete Wavelet Transform" IEEE Transactions On Circuits And Systems—Ii: Express Briefs, Vol. 59, No. 3, March 2015.

[2] Chih-Hsien Hsia, Member, IEEE, Jen-Shiun Chiang, Member, IEEE, and Jing-Ming Guo, Senior Member, IEEE "Memory-Efficient Hardware Architecture of 2-D Dual-Mode Lifting- Based Discrete Wavelet Transform" IEEE Transactions On Circuits And Systems For Video Technology, Vol. 23, No. 4, April 2014.

[3]Jinook Song, Student Member, IEEE, and In-Cheol Park, Senior Member, IEEE, "Pipelined Discrete Wavelet Transform Architecture Scanning Dual Lines" IEEE Transactions On Circuits And Systems—Ii: Express Briefs, Vol. 56, No. 12, December 2013.

[4]Yeong-Kang Lai, Member, IEEE, Lien-Fei Chen, Student Member, IEEE, and Yui-Chih Shih, "A High-Performance and Memory- Efficient VLSI Architecture with Parallel Scanning Method for 2-D Lifting Based Discrete Wavelet Transform" IEEE Transactions on Consumer Electronics, Vol. 55, No. 2, MAY 2009 Contributed Paper.

[5]Basant Kumar Mohanty, Senior Member, IEEE, and Pramod Kumar Meher, Senior Member, IEEE, "Memory-Efficient High-Speed Convolution-based Generic Structure for Multilevel 2-D DWT" IEEE Transactions On Circuits And Systems For Video Technology, Vol. 23, No. 2, February 2013.

[6] Yusong Hu, Student Member, IEEE, And ChingChuen Jong, Member, IEEE, "A Memory- Efficient High-Throughput Architecture For Lifting-Based Multi-Level 2-D Dwt" IEEE Transactions On Signal Processing, Vol. 61, No. 20, October 15, 2013.

[7] UshaBhanu.N and Dr.A. Chilambuchelvan, "A Detailed Survey on VLSI Architectures for Lifting based DWT for efficient hardware implementation" International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.2, April 2012.